因?yàn)閷I(yè)

所以領(lǐng)先

一、CoWoS封裝工藝分類及技術(shù)差異

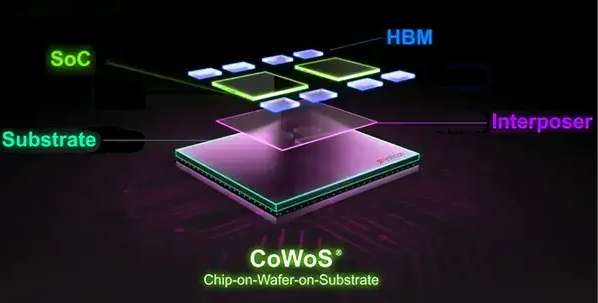

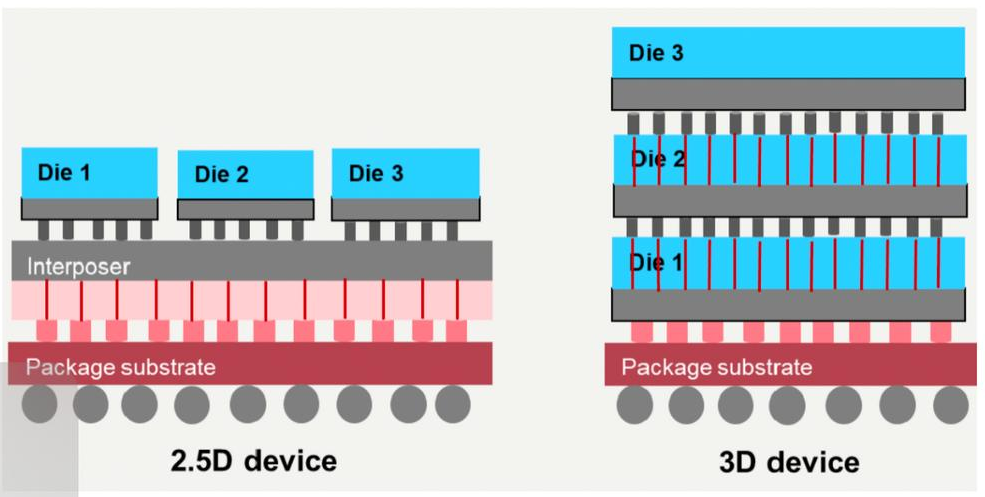

CoWoS(Chip On Wafer On Substrate)是臺(tái)積電主導(dǎo)的2.5D先進(jìn)封裝技術(shù),基于不同轉(zhuǎn)接板類型可分為CoWoS-S、CoWoS-L和CoWoS-R三大類,核心差異體現(xiàn)在中介層設(shè)計(jì)、性能參數(shù)及應(yīng)用場(chǎng)景上:

| 工藝類型 | 技術(shù)特點(diǎn) | 關(guān)鍵參數(shù) | 應(yīng)用場(chǎng)景 | 發(fā)展階段 |

| CoWoS-S | 基于硅中介層(無源轉(zhuǎn)接板),采用雙路光刻拼接法擴(kuò)大面積,集成深溝槽電容器(iCap)和亞微米銅互聯(lián)。 | - 硅中介層面積:2500mm2(相當(dāng)于3倍光罩面積) | AI算力芯片(如英偉達(dá)Hopper系列A100/H100)、HBM存儲(chǔ)集成 | 已發(fā)展至第5代(CoWoS-S5),當(dāng)前主流量產(chǎn)工藝 |

| - HBM堆棧空間:8個(gè) | ||||

| - 電容密度:>300nF/mm2 | ||||

| - 熱導(dǎo)率:20W/K(新型TIM材料) | ||||

| CoWoS-L | 采用RDL(重布線層)+本地硅互聯(lián)(LSI)替代傳統(tǒng)硅中介層,通過10+LSI小芯片拼接提升設(shè)計(jì)靈活性,兼容有機(jī)層直接連接芯片。 | - 轉(zhuǎn)接板面積:1.5倍光罩面積 | 高性能GPU(如英偉達(dá)Blackwell Ultra)、高密度計(jì)算芯片 | 2024年推出,2025Q4起將成為臺(tái)積電CoWoS主要制程 |

| - HBM堆疊能力:最多12顆HBM3 | ||||

| - 支持4個(gè)SoC+8個(gè)HBM集成 | ||||

| CoWoS-R | 進(jìn)一步擴(kuò)大中介板面積,采用非凝膠型熱界面材料,優(yōu)化熱管理和良率。 | - 中介板面積:3.3倍光罩面積(H100僅為2.2倍) | 超大規(guī)模芯片集成(未來高性能計(jì)算需求) | 技術(shù)儲(chǔ)備階段,尚未大規(guī)模量產(chǎn) |

| - 熱管理:新型TIM材料提升散熱效率 |

核心差異總結(jié):

CoWoS-S:成熟度最高,依賴硅中介層,成本較高但性能穩(wěn)定,適用于當(dāng)前AI芯片主流需求;

CoWoS-L:成本更低、設(shè)計(jì)彈性更大,通過小芯片拼接突破光罩面積限制,是未來高性能GPU的核心工藝;

CoWoS-R:面向超大規(guī)模集成場(chǎng)景,技術(shù)前瞻性強(qiáng),但需解決良率和熱管理挑戰(zhàn)。

CoWoS封裝技術(shù)的應(yīng)用場(chǎng)景高度聚焦于高算力需求領(lǐng)域,其市場(chǎng)前景與AI芯片、HBM存儲(chǔ)及云計(jì)算需求深度綁定:

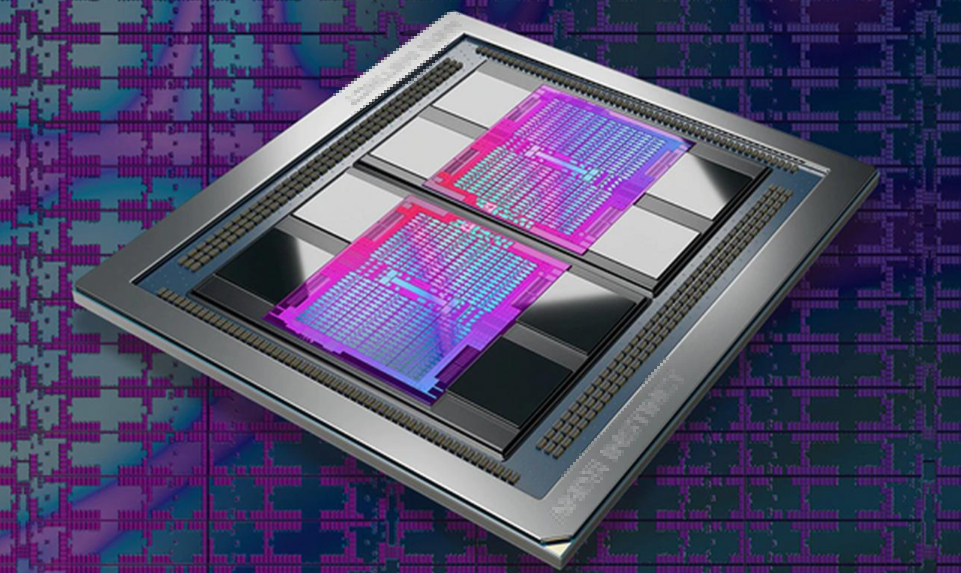

AI算力芯片:英偉達(dá)是最大需求方,其Hopper系列(A100/H100)、Blackwell系列GPU均采用CoWoS工藝,占臺(tái)積電CoWoS產(chǎn)能超50%。AMD的Instinct MI系列(如MI300)也依賴該技術(shù)。

HBM存儲(chǔ)集成:CoWoS-S5支持8個(gè)HBM堆棧,CoWoS-L可擴(kuò)展至12個(gè)HBM3,成為AI芯片高帶寬存儲(chǔ)的關(guān)鍵封裝方案。

云計(jì)算ASIC:博通、Marvell等企業(yè)通過CoWoS封裝為谷歌、亞馬遜定制ASIC芯片,滿足云端AI加速需求。

產(chǎn)能增長(zhǎng):2024年底全球CoWoS月產(chǎn)能接近4萬(wàn)片,2025年預(yù)計(jì)躍升至9.2萬(wàn)片(臺(tái)積電占8萬(wàn)片)。

需求驅(qū)動(dòng):英偉達(dá)Blackwell系列量產(chǎn)將推動(dòng)CoWoS-L滲透率提升,2025年全球AI芯片市場(chǎng)規(guī)模預(yù)計(jì)增長(zhǎng)超40%,直接拉動(dòng)CoWoS產(chǎn)能需求。

封測(cè)與設(shè)備:臺(tái)積電、日月光、安靠(Amkor)為核心產(chǎn)能供應(yīng)商,半導(dǎo)體設(shè)備(如光刻機(jī)、鍵合設(shè)備)和材料(硅中介層、TIM材料)需求激增。

國(guó)產(chǎn)替代機(jī)遇:中國(guó)CoWoS相關(guān)產(chǎn)業(yè)鏈(如封裝材料、設(shè)備)處于起步階段,隨著全球產(chǎn)能擴(kuò)張,具備國(guó)產(chǎn)化潛力。

技術(shù)迭代:CoWoS-L將逐步替代CoWoS-S成為主流,2025年占臺(tái)積電CoWoS產(chǎn)能比例預(yù)計(jì)超70%。

成本控制:硅中介層的光刻拼接良率、翹曲問題仍是產(chǎn)能瓶頸,CoWoS-L通過LSI小芯片拼接可降低對(duì)大尺寸硅中介層的依賴。

競(jìng)爭(zhēng)格局:英偉達(dá)的需求占比超50%,其產(chǎn)品迭代(如Blackwell系列)直接主導(dǎo)CoWoS技術(shù)路線,其他廠商(如博通、AMD)的份額將逐步提升。

總結(jié):CoWoS封裝技術(shù)是AI算力革命的“基礎(chǔ)設(shè)施”,CoWoS-L將成為2025年后的核心工藝,其成本優(yōu)勢(shì)和設(shè)計(jì)靈活性將推動(dòng)高性能GPU、HBM及云計(jì)算芯片的進(jìn)一步集成,同時(shí)帶動(dòng)半導(dǎo)體設(shè)備、材料等產(chǎn)業(yè)鏈環(huán)節(jié)的增長(zhǎng)。

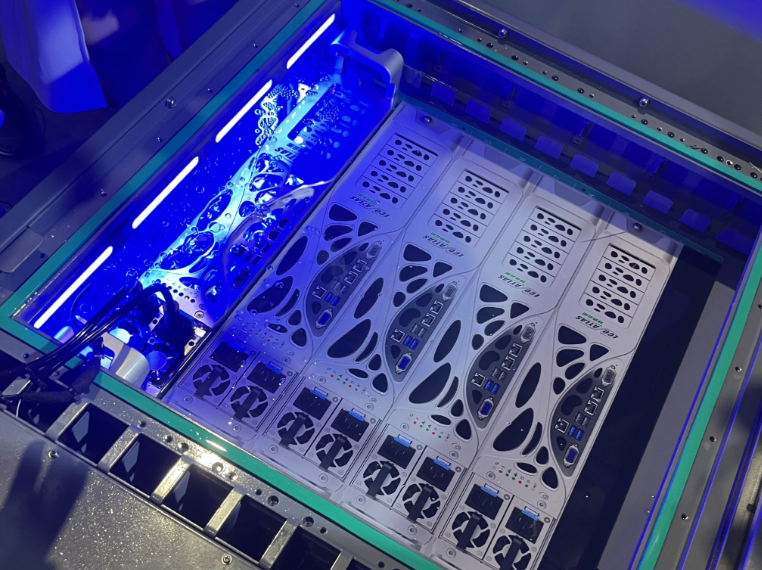

CoWoS封裝芯片清洗劑選擇:

水基清洗的工藝和設(shè)備配置選擇對(duì)清洗精密器件尤其重要,一旦選定,就會(huì)作為一個(gè)長(zhǎng)期的使用和運(yùn)行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環(huán)境中的濕氣,通電后發(fā)生電化學(xué)遷移,形成樹枝狀結(jié)構(gòu)體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長(zhǎng)枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內(nèi)的浮點(diǎn)、灰塵、塵埃等,這些污染物會(huì)導(dǎo)致焊點(diǎn)質(zhì)量降低、焊接時(shí)焊點(diǎn)拉尖、產(chǎn)生氣孔、短路等等多種不良現(xiàn)象。

這么多污染物,到底哪些才是最備受關(guān)注的呢?助焊劑或錫膏普遍應(yīng)用于回流焊和波峰焊工藝中,它們主要由溶劑、潤(rùn)濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質(zhì)在所有污染物中的占據(jù)主導(dǎo),從產(chǎn)品失效情況來而言,焊后殘余物是影響產(chǎn)品質(zhì)量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質(zhì)引發(fā)接觸電阻增大,嚴(yán)重者導(dǎo)致開路失效,因此焊后必須進(jìn)行嚴(yán)格的清洗,才能保障電路板的質(zhì)量。

合明科技研發(fā)的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

合明科技運(yùn)用自身原創(chuàng)的產(chǎn)品技術(shù),滿足芯片封裝工藝制程清洗的高難度技術(shù)要求,打破國(guó)外廠商在行業(yè)中的壟斷地位,為芯片封裝材料全面國(guó)產(chǎn)自主提供強(qiáng)有力的支持。

推薦使用合明科技水基清洗劑產(chǎn)品。

![[x]](/template/default/picture/closeimgfz1.svg)