因為專業

所以領先

這是一個關于芯片封裝技術的詳細解答,涵蓋了常規傳統封裝、先進封裝以及它們的優缺點分析。

常規封裝主要完成三個核心功能:保護(保護晶圓上的脆弱芯片)、供電(為芯片提供穩定電源)、連接(實現芯片與外部電路板的電氣互聯和信號傳輸)。其特點是封裝體通常比芯片本身大得多,引腳從封裝體側面或底部引出。

主要工藝類型:

DIP (Dual In-line Package) - 雙列直插式封裝

描述:最早的封裝形式之一,引腳從封裝體兩側引出,呈直線排列,需要插入到PCB板的插座中或直接焊通孔。

優點:牢固可靠,適合手工焊接和檢測,成本極低。

缺點:體積龐大,引腳數受限(通常少于100個),頻率性能差,不適合高密度集成。

應用:早期的CPU、內存條、微控制器及其它通用集成電路,現在多用于教學、實驗或低端消費電子。

SOP/SOIC (Small Outline Package) - 小外形封裝

描述:DIP的表面貼裝(SMT)版本,引腳從封裝體兩側引出,但引腳為“鷗翼形”(Gull Wing),直接貼在PCB表面。

優點:比DIP體積小,重量輕,適合高密度表面貼裝,生產效率高。

缺點:引腳數仍然受限(通常少于100個)。

應用:各種常見的集成電路,如運算放大器、邏輯門電路等。

QFP (Quad Flat Package) - 四側引腳扁平封裝

描述:在SOP基礎上的擴展,引腳從封裝體的四個側面引出,同樣是“鷗翼形”引腳。

優點:在相同體積下,比SOP能容納更多的引腳(可達數百個)。

缺點:引腳間距(Pitch)較小時,焊接難度增加,容易短路。對PCB的貼裝精度要求高。

應用:微控制器、處理器、早期的芯片組等。

PGA (Pin Grid Array) - 插針網格陣列封裝

描述:封裝底部是陣列式的插針,而不是四周的引腳。需要插入到主板上的插座中(如經典的Intel CPU封裝)。

優點:在相同面積下,比周邊引腳的封裝方式能提供更多的I/O數量,散熱較好。

缺點:插拔式設計,長期使用可能接觸不良;插針容易彎曲;體積仍然較大。

應用:早期的Intel Pentium、AMD Athlon等CPU。

BGA (Ball Grid Array) - 球柵陣列封裝

檢測維修困難:焊點不可見,必須使用X光或專用檢測設備,返修需要專用工具。

I/O密度高:底部全平面布局,能容納遠多于QFP的I/O數量。

電性能好:引腳路徑短,電感小,更適合高頻高速信號。

可靠性高:焊點隱藏在封裝體下方,受到保護,不易損壞。

散熱好:芯片背面常可接觸散熱器,且部分BGA封裝基板內自帶散熱片。

描述:是傳統封裝向先進封裝過渡的關鍵技術。它將封裝體四周的引腳變為封裝底部的焊球陣列。

優點:

缺點:

應用:幾乎所有現代CPU、GPU、手機主芯片、高端微控制器等。是當前最主流的封裝技術之一。

先進封裝不再滿足于簡單的“保護與連接”,而是追求更高性能、更高密度、更小尺寸、更低功耗和異質集成。其核心特點是封裝體尺寸接近甚至小于芯片本身,并開始涉及芯片級別的互連和整合。

主要工藝類型:

FC (Flip Chip) - 倒裝芯片

互連路徑極短,電性能極佳,寄生效應小。

散熱性能更好,熱量可通過凸點直接傳導到基板。

I/O密度可以做得非常高。

描述:是絕大多數先進封裝的基礎。與傳統“正裝”(芯片正面朝上,通過線鍵合Wire Bonding連接)不同,Flip Chip將芯片正面朝下,通過芯片上的凸塊(Bump)直接與基板或另一顆芯片連接。

優點:

缺點:工藝復雜,成本高;需要額外的底部填充(Underfill)工藝來加固焊點,抵抗熱應力。

應用:作為基礎技術,廣泛應用于BGA、WLP、2.5D/3D等幾乎所有先進封裝中。

WLP (Wafer Level Package) - 晶圓級封裝

尺寸最小,極大地節省了空間。

生產效率高,可以并行處理整片晶圓上的所有芯片。

電性能好,互連路徑短。

描述:直接在整片晶圓上完成所有的封裝工序(如植球、測試),最后再切割成單個芯片。封裝后的尺寸幾乎和芯片一樣大,稱為“Chip Scale Package (CSP)”。

優點:

缺點:封裝體與芯片尺寸相同,散熱和機械保護能力相對較弱。

應用:智能手機、可穿戴設備中的射頻芯片、電源管理芯片、傳感器等空間受限的領域。

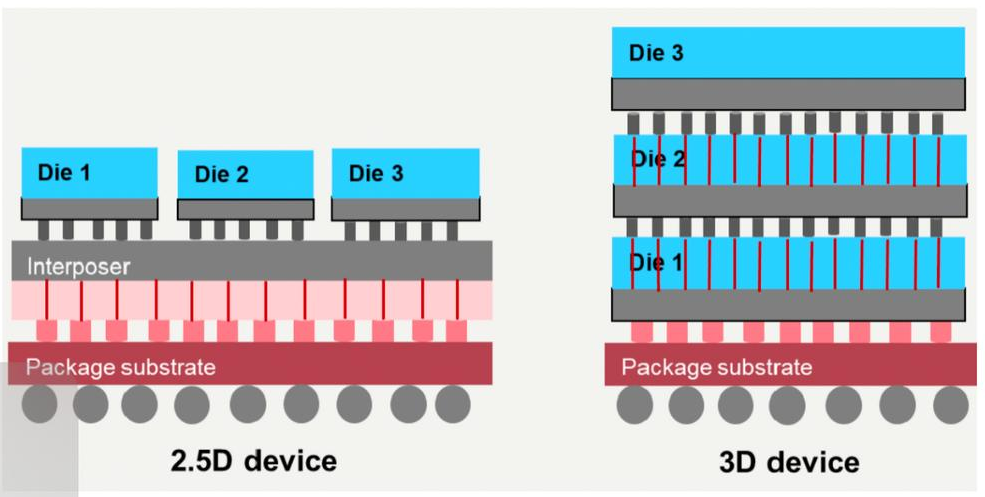

2.5D封裝

實現了不同工藝、不同功能芯片(如CPU、HBM內存、GPU)的高性能異質集成。

互連密度和帶寬遠高于傳統PCB,延遲更低。

描述:將多顆芯片并排放置在一個硅中介層(Silicon Interposer) 上。中介層內部有高密度的硅通孔(TSV)和布線,充當一個“超級高速公路”,實現芯片間的高速互連,最后再將中介層封裝到基板上。

優點:

缺點:引入了中介層,成本非常高,設計復雜。

應用:高端GPU(如NVIDIA的CoWoS系列)、AI加速卡、FPGA(如Xilinx Virtex-7)等。

3D封裝

HBM(高帶寬內存):將多個DRAM芯片堆疊在一起,通過TSV與GPU/CPU互聯。

SoIC、X-Cube:將處理器、緩存等邏輯芯片進行3D堆疊。

集成度最高,極大縮短了芯片間互連長度,速度和帶寬達到極致,功耗更低。

實現了真正的“超越摩爾”。

描述:將多顆芯片在垂直方向上堆疊起來,并通過TSV(Through-Silicon Via,硅通孔) 直接實現縱向互連,就像蓋高樓一樣。

優點:

缺點:技術難度和成本最高;散熱是巨大挑戰。

應用:

SiP (System in Package) - 系統級封裝

功能完整性,可集成任何類型的芯片和元件。

設計靈活,開發周期短于SoC。

小型化。

描述:一種集成理念,將多個不同功能的芯片(如處理器、內存、射頻、無源器件等)通過任何方式(Wire Bonding、Flip Chip、甚至嵌入基板)集成在一個封裝體內,形成一個完整的系統或子系統。

優點:

缺點:系統級設計和測試復雜。

應用:蘋果手表S系列芯片(將AP、內存、存儲等集成一體)、射頻模塊、物聯網模組。

| 封裝類型 | 優點 | 缺點 | 典型應用 |

| 傳統封裝 (如QFP) | 成本低、工藝成熟、檢測維修方便 | I/O密度低、體積大、電性能差、頻率受限 | 通用IC、低端微控制器 |

| BGA | I/O密度高、電性能好、可靠性高、散熱佳 | 焊點隱藏,檢測和返修困難 | 主流CPU、GPU、手機SoC |

| WLP | 尺寸極小、電性能優異、生產效率高 | 散熱和機械強度較弱 | 移動設備、可穿戴設備中的小芯片 |

| 2.5D/3D | 極致性能、超高密度、異質集成、低延遲高帶寬 | 成本極高、設計極其復雜、散熱挑戰巨大 | 頂級AI芯片、HBM內存、高性能計算 |

| SiP | 高度功能集成、設計靈活、開發周期短、小型化 | 系統級測試復雜,成本高于單芯片 | 復雜系統模組(如智能手表芯片、射頻前端) |

傳統封裝:追求成本效益和可靠性,滿足基本功能需求。

先進封裝:追求性能極限和功能整合,是延續摩爾定律生命、超越摩爾定律的關鍵路徑。

發展趨勢:從二維平面互連走向三維立體堆疊;從單一芯片封裝走向多芯片異質集成;從“大封裝”走向“芯片即封裝”的晶圓級系統整合。先進封裝正在成為提升芯片整體性能的主戰場。

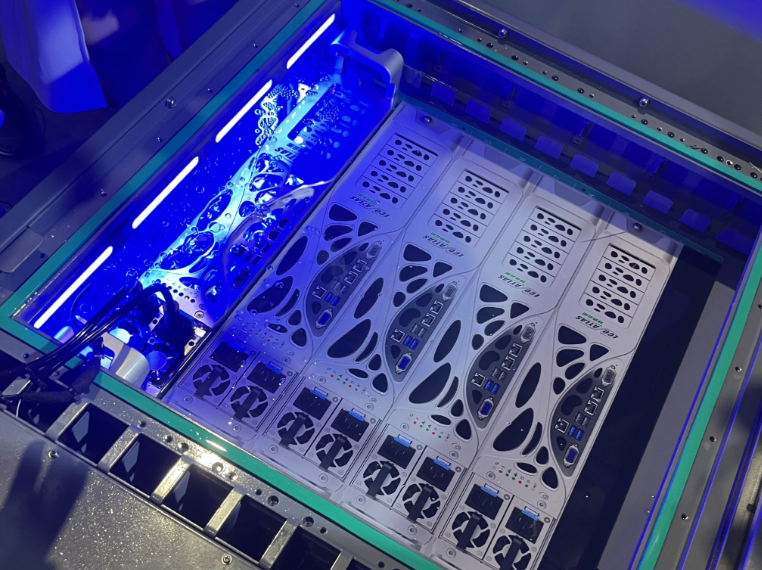

上一篇:浸沒式液冷服務器優缺點與應用分析及液冷服務器電路···

下一篇:沒有了!

![[x]](/template/default/picture/closeimgfz1.svg)