因?yàn)閷I(yè)

所以領(lǐng)先

下一代半導(dǎo)體封裝生產(chǎn)工藝主要包括以下5種技術(shù),其核心特點(diǎn)及發(fā)展趨勢如下:

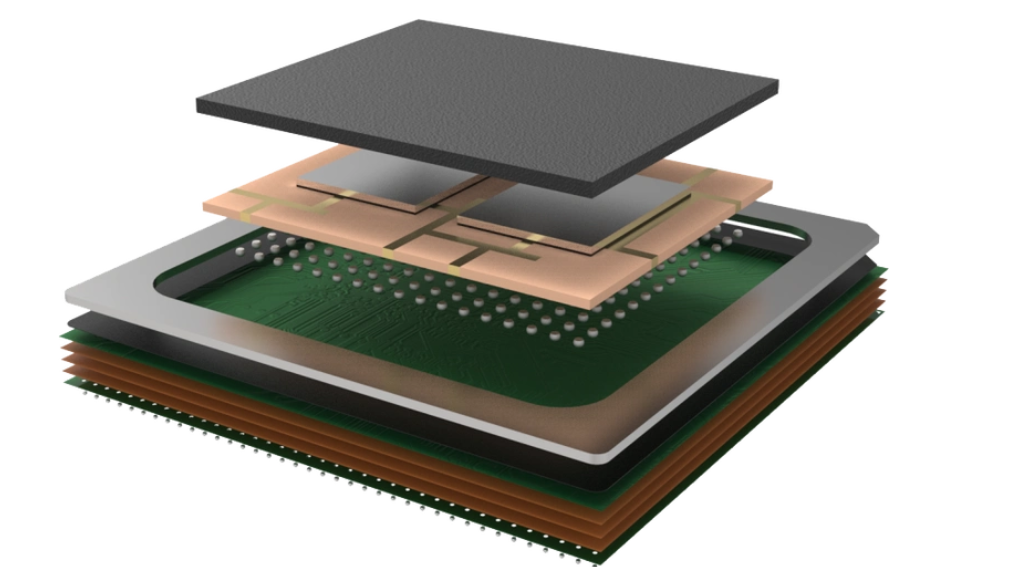

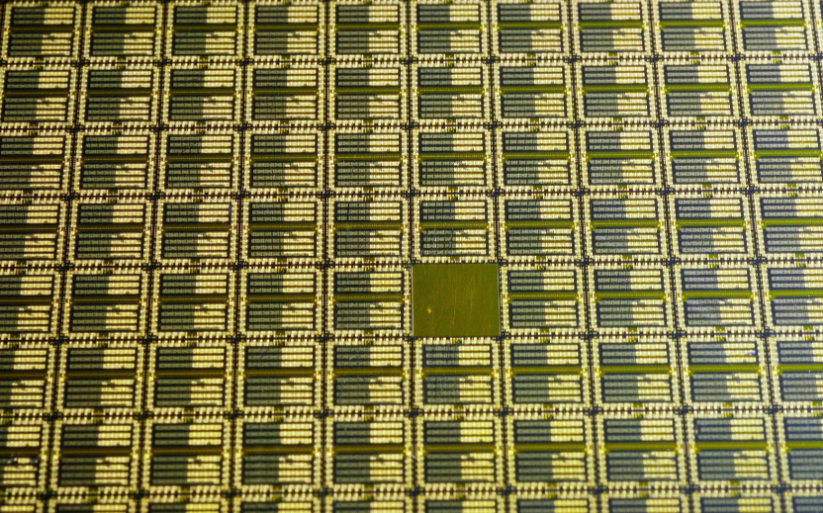

技術(shù)特點(diǎn):通過垂直堆疊多層芯片或晶圓,利用硅通孔(TSV)實(shí)現(xiàn)立體互連,顯著提升集成密度和信號傳輸效率。例如,HBM存儲(chǔ)器采用3D堆疊技術(shù)實(shí)現(xiàn)超高速數(shù)據(jù)傳輸。

優(yōu)勢:縮短互連距離(降低40%延遲)、減少功耗(優(yōu)化30%以上)、支持異構(gòu)集成(如邏輯芯片+存儲(chǔ)器組合)。

挑戰(zhàn):熱管理難度高,需開發(fā)高效散熱結(jié)構(gòu);TSV加工精度要求納米級,成本較高。

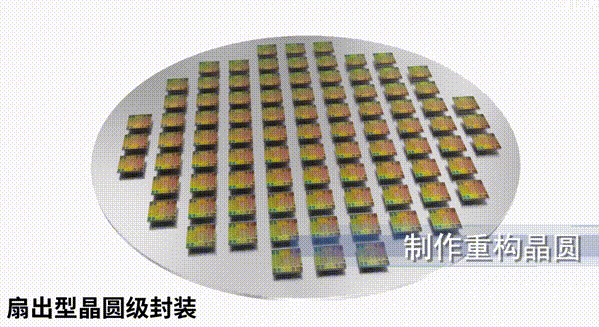

技術(shù)特點(diǎn):在晶圓級直接完成封裝,通過重新分布層(RDL)將I/O端口擴(kuò)展至芯片外部區(qū)域,無需傳統(tǒng)基板。

優(yōu)勢:封裝尺寸接近芯片實(shí)際大小(節(jié)省50%以上空間),支持多芯片異構(gòu)集成,成本比傳統(tǒng)封裝低30%。

應(yīng)用場景:5G射頻模塊、移動(dòng)處理器(如蘋果A系列芯片)。

技術(shù)特點(diǎn):將處理器、存儲(chǔ)器、傳感器等多顆芯片集成于單一封裝內(nèi),實(shí)現(xiàn)完整系統(tǒng)功能。

優(yōu)勢:縮短系統(tǒng)開發(fā)周期(減少50%設(shè)計(jì)時(shí)間),支持柔性配置(如物聯(lián)網(wǎng)設(shè)備的定制化需求)。

典型案例:蘋果Watch的S系列芯片集成生物傳感器和通信模塊。

技術(shù)特點(diǎn):將芯片嵌入印刷電路板(PCB)內(nèi)部,通過埋入式布線實(shí)現(xiàn)高密度互連。

優(yōu)勢:提升散熱效率(導(dǎo)熱性能提高20%),增強(qiáng)機(jī)械穩(wěn)定性(抗振動(dòng)能力優(yōu)于傳統(tǒng)封裝)。

應(yīng)用領(lǐng)域:汽車電子(如ECU控制模塊)、工業(yè)設(shè)備。

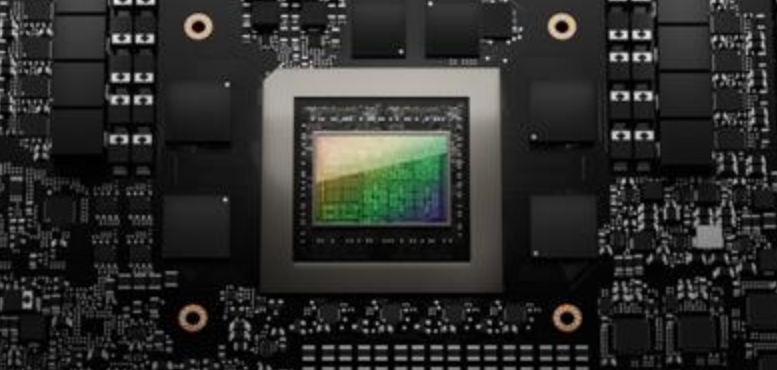

技術(shù)特點(diǎn):采用硅中介層(Interposer)實(shí)現(xiàn)芯片間高速互連,支持2.5D平面集成或3D垂直堆疊。

優(yōu)勢:帶寬提升至TB/s級別(如HBM3存儲(chǔ)器),兼容不同工藝節(jié)點(diǎn)芯片的混合集成。

挑戰(zhàn):中介層制造成本高,需解決熱應(yīng)力導(dǎo)致的界面可靠性問題。

| 技術(shù)類型 | 集成密度 | 成本效益 | 典型應(yīng)用場景 | 引用來源 |

|---|---|---|---|---|

| 3D ICs | ★★★★★ | ★★☆ | 高性能計(jì)算/AI芯片 | |

| Fan-Out WLP | ★★★★☆ | ★★★★ | 移動(dòng)設(shè)備/射頻模塊 | |

| SiP | ★★★☆ | ★★★☆ | 物聯(lián)網(wǎng)/可穿戴設(shè)備 | |

| 嵌入式封裝 | ★★★☆ | ★★★★ | 汽車電子/工業(yè)控制 | |

| 2.5D中介層 | ★★★★☆ | ★★☆ | 數(shù)據(jù)中心/GPU加速卡 |

未來發(fā)展方向?qū)⒕劢褂诙喙δ芗桑ㄈ绻怆姽卜庋b)、綠色制造(減少重金屬使用)和智能化工藝(AI驅(qū)動(dòng)的缺陷檢測)。需進(jìn)一步了解具體工藝細(xì)節(jié),可查閱引用文獻(xiàn)中的技術(shù)解析。

![[x]](/template/default/picture/closeimgfz1.svg)